डिझाइनफोटोनिकएकात्मिक सर्किट

फोटोनिक एकात्मिक सर्किट्सइंटरफेरोमीटरमध्ये किंवा मार्गाच्या लांबीसाठी संवेदनशील असलेल्या इतर अनुप्रयोगांमध्ये मार्गाच्या लांबीचे महत्त्व असल्यामुळे, (PIC) ची रचना अनेकदा गणितीय स्क्रिप्ट्सच्या मदतीने केली जाते.चित्रएका वेफरवर अनेक थर (साधारणपणे १० ते ३०) नक्षीकाम करून तयार केले जाते, जे अनेक बहुभुजी आकारांनी बनलेले असतात आणि बहुतेकदा GDSII स्वरूपात दर्शविले जातात. फोटोमास्क उत्पादकाला फाईल पाठवण्यापूर्वी, डिझाइनची अचूकता तपासण्यासाठी PIC चे सिम्युलेशन करणे अत्यंत इष्ट आहे. सिम्युलेशन अनेक स्तरांमध्ये विभागलेले आहे: सर्वात खालचा स्तर म्हणजे त्रिमितीय विद्युतचुंबकीय (EM) सिम्युलेशन, जिथे सिम्युलेशन उप-तरंगलांबी स्तरावर केले जाते, जरी पदार्थातील अणूंमधील आंतरक्रिया स्थूल स्तरावर हाताळल्या जातात. सामान्य पद्धतींमध्ये त्रिमितीय फायनाइट-डिफरन्स टाइम-डोमेन (3D FDTD) आणि आयगेनमोड एक्सपान्शन (EME) यांचा समावेश होतो. या पद्धती सर्वात अचूक आहेत, परंतु संपूर्ण PIC सिम्युलेशन वेळेसाठी अव्यवहार्य आहेत. पुढचा स्तर २.५-मितीय EM सिम्युलेशन आहे, जसे की फायनाइट-डिफरन्स बीम प्रोपगेशन (FD-BPM). या पद्धती खूप वेगवान आहेत, परंतु त्या अचूकतेशी तडजोड करतात आणि केवळ पॅराएक्सियल प्रसारण हाताळू शकतात व उदाहरणार्थ, रेझोनेटरचे सिम्युलेशन करण्यासाठी वापरल्या जाऊ शकत नाहीत. पुढचा स्तर म्हणजे २डी ईएम सिम्युलेशन, जसे की २डी एफडीटीडी आणि २डी बीपीएम. या देखील वेगवान आहेत, परंतु त्यांची कार्यक्षमता मर्यादित आहे, जसे की त्या पोलरायझेशन रोटेटरचे सिम्युलेशन करू शकत नाहीत. पुढील स्तर म्हणजे ट्रान्समिशन आणि/किंवा स्कॅटरिंग मॅट्रिक्स सिम्युलेशन. प्रत्येक प्रमुख घटक इनपुट आणि आउटपुट असलेल्या घटकामध्ये रूपांतरित केला जातो आणि जोडलेला वेव्हगाइड फेज शिफ्ट आणि अॅटेन्युएशन घटकामध्ये रूपांतरित केला जातो. ही सिम्युलेशन्स अत्यंत वेगवान असतात. ट्रान्समिशन मॅट्रिक्सला इनपुट सिग्नलने गुणून आउटपुट सिग्नल मिळवला जातो. स्कॅटरिंग मॅट्रिक्स (ज्याच्या घटकांना एस-पॅरामीटर्स म्हणतात) घटकाच्या एका बाजूचे इनपुट आणि आउटपुट सिग्नल गुणून दुसऱ्या बाजूचे इनपुट आणि आउटपुट सिग्नल शोधतो. मुळात, स्कॅटरिंग मॅट्रिक्समध्ये घटकाच्या आतील परावर्तन समाविष्ट असते. स्कॅटरिंग मॅट्रिक्स सामान्यतः प्रत्येक मितीमध्ये ट्रान्समिशन मॅट्रिक्सपेक्षा दुप्पट मोठा असतो. थोडक्यात, 3D EM पासून ट्रान्समिशन/स्कॅटरिंग मॅट्रिक्स सिम्युलेशनपर्यंत, सिम्युलेशनच्या प्रत्येक स्तरावर वेग आणि अचूकता यांच्यात तडजोड करावी लागते, आणि डिझाइनर डिझाइन प्रमाणीकरण प्रक्रिया ऑप्टिमाइझ करण्यासाठी त्यांच्या विशिष्ट गरजांनुसार सिम्युलेशनचा योग्य स्तर निवडतात.

तथापि, विशिष्ट घटकांच्या इलेक्ट्रोमॅग्नेटिक सिम्युलेशनवर अवलंबून राहणे आणि संपूर्ण PIC चे सिम्युलेशन करण्यासाठी स्कॅटरिंग/ट्रान्सफर मॅट्रिक्स वापरणे, हे फ्लो प्लेटसमोर पूर्णपणे अचूक डिझाइनची हमी देत नाही. उदाहरणार्थ, चुकीच्या पद्धतीने मोजलेली मार्गाची लांबी, उच्च-ऑर्डर मोड्सना प्रभावीपणे दाबण्यात अयशस्वी होणारे मल्टीमोड वेव्हगाइड्स, किंवा एकमेकांच्या खूप जवळ असलेले दोन वेव्हगाइड्स ज्यामुळे अनपेक्षित कपलिंग समस्या निर्माण होतात, या गोष्टी सिम्युलेशन दरम्यान लक्षात न येण्याची शक्यता असते. म्हणून, जरी प्रगत सिम्युलेशन साधने शक्तिशाली डिझाइन प्रमाणीकरण क्षमता प्रदान करत असली तरी, डिझाइनची अचूकता आणि विश्वसनीयता सुनिश्चित करण्यासाठी आणि फ्लो शीटचा धोका कमी करण्यासाठी, डिझाइनरकडून व्यावहारिक अनुभव आणि तांत्रिक ज्ञानासह उच्च पातळीची दक्षता आणि काळजीपूर्वक तपासणी आवश्यक असते.

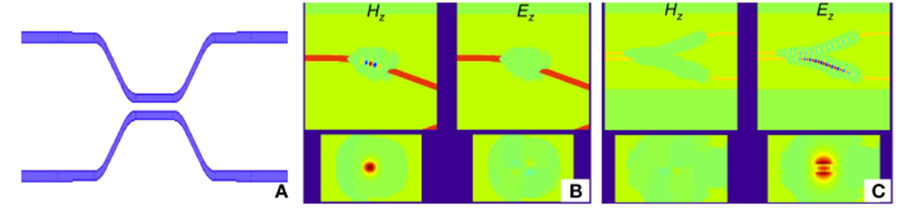

स्पार्स एफडीटीडी (sparse FDTD) नावाचे एक तंत्र, डिझाइनची पडताळणी करण्यासाठी संपूर्ण पीआयसी (PIC) डिझाइनवर थेट ३डी आणि २डी एफडीटीडी सिम्युलेशन करण्यास अनुमती देते. जरी कोणत्याही इलेक्ट्रोमॅग्नेटिक सिम्युलेशन टूलसाठी खूप मोठ्या आकाराच्या पीआयसीचे सिम्युलेशन करणे कठीण असले तरी, स्पार्स एफडीटीडी एका बऱ्यापैकी मोठ्या स्थानिक क्षेत्राचे सिम्युलेशन करण्यास सक्षम आहे. पारंपरिक ३डी एफडीटीडीमध्ये, एका विशिष्ट क्वांटाइज्ड व्हॉल्यूममध्ये इलेक्ट्रोमॅग्नेटिक फील्डचे सहा घटक इनिशिअलाइज करून सिम्युलेशन सुरू होते. जसजसा वेळ पुढे जातो, तसतसे व्हॉल्यूममधील नवीन फील्ड घटकाची गणना केली जाते, आणि ही प्रक्रिया पुढे चालू राहते. प्रत्येक टप्प्यासाठी खूप गणना करावी लागते, त्यामुळे बराच वेळ लागतो. स्पार्स ३डी एफडीटीडीमध्ये, व्हॉल्यूमच्या प्रत्येक बिंदूवर प्रत्येक टप्प्यावर गणना करण्याऐवजी, फील्ड घटकांची एक सूची ठेवली जाते जी सैद्धांतिकदृष्ट्या कोणत्याही मोठ्या व्हॉल्यूमशी संबंधित असू शकते आणि केवळ त्या घटकांसाठीच गणना केली जाते. प्रत्येक टाइम स्टेपवर, फील्ड घटकांना लागून असलेले बिंदू जोडले जातात, तर एका विशिष्ट पॉवर थ्रेशोल्डच्या खाली असलेले फील्ड घटक वगळले जातात. काही संरचनांसाठी, ही गणना पारंपरिक ३डी एफडीटीडीपेक्षा कित्येक पटीने अधिक वेगवान असू शकते. तथापि, विखुरलेल्या संरचना हाताळताना विरळ FDTDs चांगली कामगिरी करत नाहीत, कारण यामुळे टाइम फील्ड खूप जास्त पसरते, परिणामी याद्या खूप लांब आणि व्यवस्थापित करण्यास कठीण होतात. आकृती १ मध्ये पोलरायझेशन बीम स्प्लिटर (PBS) सारख्या ३डी FDTD सिम्युलेशनचा एक उदाहरण स्क्रीनशॉट दाखवला आहे.

आकृती १: ३डी स्पार्स एफडीटीडी (3D sparse FDTD) मधील सिम्युलेशनचे परिणाम. (A) हे सिम्युलेट केल्या जाणाऱ्या संरचनेचे वरून दिसणारे दृश्य आहे, जी एक डायरेक्शनल कपलर आहे. (B) क्वासी-टीई (quasi-TE) एक्सायटेशन वापरून केलेल्या सिम्युलेशनचा स्क्रीनशॉट दाखवते. वरील दोन आकृत्या क्वासी-टीई आणि क्वासी-टीएम (quasi-TM) सिग्नल्सचे वरून दिसणारे दृश्य दाखवतात, आणि खालील दोन आकृत्या संबंधित क्रॉस-सेक्शनल दृश्य दाखवतात. (C) क्वासी-टीएम एक्सायटेशन वापरून केलेल्या सिम्युलेशनचा स्क्रीनशॉट दाखवते.

पोस्ट करण्याची वेळ: जुलै-२३-२०२४