वापरूनऑप्टोइलेक्ट्रॉनिकमोठ्या प्रमाणात डेटा ट्रान्समिशनची समस्या सोडवण्यासाठी को-पॅकेजिंग तंत्रज्ञान

संगणकीय शक्तीच्या उच्च स्तरावरील विकासामुळे, डेटाचे प्रमाण झपाट्याने वाढत आहे, विशेषतः एआय लार्ज मॉडेल्स आणि मशीन लर्निंग सारख्या नवीन डेटा सेंटर व्यावसायिक ट्रॅफिकमुळे एंड-टू-एंड आणि वापरकर्त्यांपर्यंत डेटाच्या वाढीला चालना मिळत आहे. प्रचंड डेटा सर्व दिशांना वेगाने हस्तांतरित करणे आवश्यक आहे, आणि वाढत्या संगणकीय शक्ती व डेटा इंटरॅक्शनच्या गरजा पूर्ण करण्यासाठी डेटा ट्रान्समिशन रेट देखील 100GbE पासून 400GbE किंवा अगदी 800GbE पर्यंत विकसित झाला आहे. लाइन रेट्स वाढल्यामुळे, संबंधित हार्डवेअरची बोर्ड-स्तरीय गुंतागुंत मोठ्या प्रमाणात वाढली आहे, आणि पारंपरिक I/O प्रणाली ASics पासून फ्रंट पॅनलपर्यंत हाय-स्पीड सिग्नल्स प्रसारित करण्याच्या विविध मागण्या पूर्ण करण्यास असमर्थ ठरली आहे. या संदर्भात, CPO ऑप्टोइलेक्ट्रॉनिक को-पॅकेजिंगला मागणी आहे.

डेटा प्रोसेसिंगच्या मागणीत मोठी वाढ, सीपीओऑप्टोइलेक्ट्रॉनिकसह-सील लक्ष

ऑप्टिकल कम्युनिकेशन सिस्टीममध्ये, ऑप्टिकल मॉड्यूल आणि AISC (नेटवर्क स्विचिंग चिप) स्वतंत्रपणे पॅकेज केलेले असतात, आणिऑप्टिकल मॉड्यूलस्विचच्या फ्रंट पॅनलला प्लगेबल मोडमध्ये जोडलेले असते. प्लगेबल मोड नवीन नाही, आणि अनेक पारंपरिक I/O कनेक्शन्स याच मोडमध्ये एकत्र जोडली जातात. तांत्रिक दृष्ट्या प्लगेबल हा अजूनही पहिला पर्याय असला तरी, उच्च डेटा दरांवर प्लगेबल मोडमध्ये काही समस्या समोर आल्या आहेत, आणि जसा डेटा प्रोसेसिंगचा वेग आणखी वाढण्याची गरज असते, तसे ऑप्टिकल डिव्हाइस आणि सर्किट बोर्डमधील कनेक्शनची लांबी, सिग्नल ट्रान्समिशनमधील घट, वीज वापर आणि गुणवत्ता मर्यादित होतात.

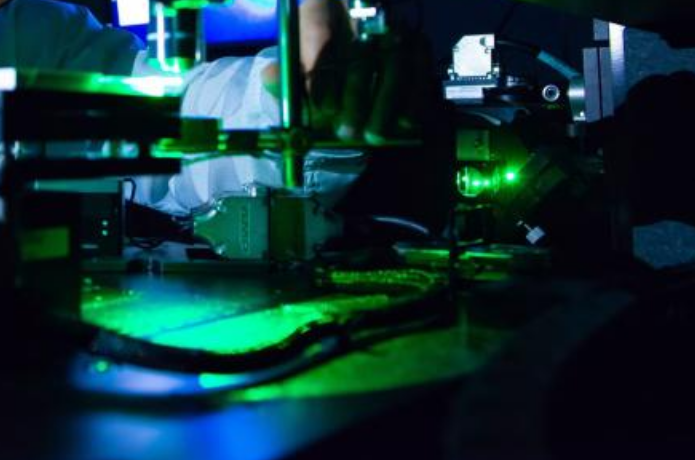

पारंपारिक कनेक्टिव्हिटीच्या मर्यादा दूर करण्यासाठी, CPO ऑप्टोइलेक्ट्रॉनिक को-पॅकेजिंगकडे लक्ष वेधले जाऊ लागले आहे. को-पॅकेज्ड ऑप्टिक्समध्ये, ऑप्टिकल मॉड्यूल्स आणि AISC (नेटवर्क स्विचिंग चिप्स) एकत्र पॅकेज केले जातात आणि कमी अंतराच्या इलेक्ट्रिकल कनेक्शनद्वारे जोडले जातात, ज्यामुळे कॉम्पॅक्ट ऑप्टोइलेक्ट्रॉनिक इंटिग्रेशन साध्य होते. CPO फोटोइलेक्ट्रॉनिक को-पॅकेजिंगमुळे मिळणारे आकार आणि वजनाचे फायदे स्पष्ट आहेत, आणि त्यामुळे हाय-स्पीड ऑप्टिकल मॉड्यूल्सचे लघुकरण आणि आकार लहान करणे शक्य होते. ऑप्टिकल मॉड्यूल आणि AISC (नेटवर्क स्विचिंग चिप) बोर्डवर अधिक केंद्रीकृत केले जातात, आणि फायबरची लांबी मोठ्या प्रमाणात कमी केली जाऊ शकते, याचा अर्थ ट्रान्समिशन दरम्यान होणारे नुकसान कमी केले जाऊ शकते.

अयार लॅब्सच्या चाचणी डेटानुसार, प्लगेबल ऑप्टिकल मॉड्यूल्सच्या तुलनेत CPO ऑप्टो-को-पॅकेजिंगमुळे वीज वापर थेट निम्म्याने कमी होऊ शकतो. ब्रॉडकॉमच्या गणनेनुसार, 400G प्लगेबल ऑप्टिकल मॉड्यूलवर, CPO योजनेमुळे वीज वापरात सुमारे 50% बचत होऊ शकते आणि 1600G प्लगेबल ऑप्टिकल मॉड्यूलच्या तुलनेत, CPO योजनेमुळे अधिक वीज बचत होते. अधिक केंद्रीकृत मांडणीमुळे इंटरकनेक्शनची घनता मोठ्या प्रमाणात वाढते, विद्युत सिग्नलमधील विलंब आणि विकृती सुधारते, आणि पारंपारिक प्लगेबल मोडप्रमाणे ट्रान्समिशन गतीवर मर्यादा राहत नाही.

दुसरा मुद्दा खर्चाचा आहे. आजच्या कृत्रिम बुद्धिमत्ता, सर्व्हर आणि स्विच सिस्टीम्सना अत्यंत उच्च घनता आणि गतीची आवश्यकता असते, आणि सध्याची मागणी वेगाने वाढत आहे. CPO को-पॅकेजिंगचा वापर न करता, ऑप्टिकल मॉड्यूलला जोडण्यासाठी मोठ्या संख्येने उच्च-स्तरीय कनेक्टर्सची आवश्यकता असते, जो एक मोठा खर्च आहे. CPO को-पॅकेजिंगमुळे कनेक्टर्सची संख्या कमी होते, ज्यामुळे BOM (बिल ऑफ मटेरियल) कमी होण्यासही मोठा हातभार लागतो. उच्च गती, उच्च बँडविड्थ आणि कमी ऊर्जा वापरणारे नेटवर्क साध्य करण्याचा CPO फोटोइलेक्ट्रिक को-पॅकेजिंग हा एकमेव मार्ग आहे. सिलिकॉन फोटोइलेक्ट्रिक घटक आणि इलेक्ट्रॉनिक घटक एकत्र पॅकेज करण्याचे हे तंत्रज्ञान ऑप्टिकल मॉड्यूलला नेटवर्क स्विच चिपच्या शक्य तितके जवळ आणते, ज्यामुळे चॅनल लॉस आणि इम्पेडन्समधील विसंगती कमी होते, इंटरकनेक्शनची घनता मोठ्या प्रमाणात सुधारते आणि भविष्यात उच्च दराच्या डेटा कनेक्शनसाठी तांत्रिक आधार मिळतो.

पोस्ट करण्याची वेळ: ०१-एप्रिल-२०२४